It’s time to highlight another key partner in the NanoIC project, this time shining the light on the Fraunhofer Institute for Reliability and Microintegration (IZM) in Berlin.

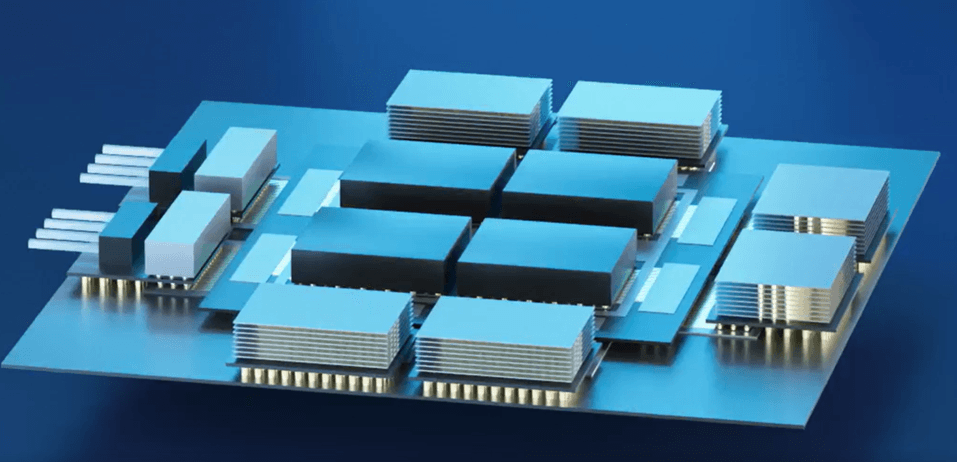

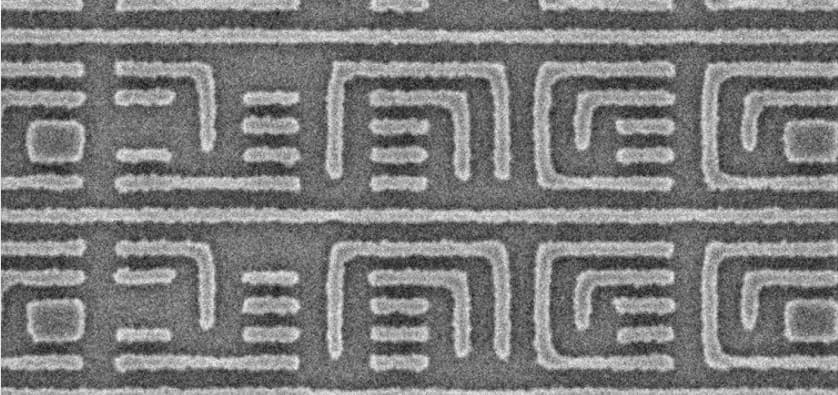

Fraunhofer IZM and imec are teaming up to initiate a pilot line for RDL First Fan-Out Wafer-Level Packaging (FOWLP) within the NanoIC project. This collaboration creates a strong partnership focused on developing high-density RDL-first FOWLP technology, critical for efficient chiplet integration in advanced computing applications.

Both Fraunhofer IZM and imec possess the needed infrastructure, combining the complementary technology building blocks to complete the whole value chain:

- Imec: High-density RDL and ultra-thin die assembly

- Fraunhofer IZM: Singulated chiplet μ-bumping (for MPW chiplets integration), thin-die assembly, molding and packaging, and reliability assessment

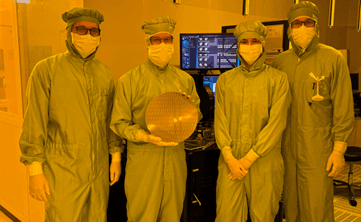

As shown on the picture, the first wafers have arrived at Fraunhofer IZM for electrical testing and further processing, a crucial step to define process standards, in-line metrology output mapping of KGD and linking this to test environments. This objective is split into two entities, the first focusing on process and in-line data capability, the second on the creation of standard electrical testing and die traceability.

Additionally, wafer molding processes on 300 mm have been set up to provide enhanced protection of the chiplets on interposers.

Beside Fraunhofer IZM, the Fraunhofer Institutes IMWS and ENAS are part of the project as well. They will soon join the spotlight in another post with their contributions to NanoIC.

The NanoIC pilot line is a pan-European effort hosted by imec, in collaboration with CEA-Leti, Fraunhofer-Gesellschaft, VTT, Tyndall National Institute, and CSSNT-UPB. Together, we are building Europe’s most advanced semiconductor R&D and prototyping infrastructure for beyond-2nm technologies.

More partner updates will follow regularly.

Published on:

18 December 2025